January 20, 2014

### Embedded Tech Trends 2014

# The Rising Importance of Signal Integrity in VPX systems

Matt McAlonis- Development Engineering Manager

**EVERY CONNECTION COUNTS**

### Consumer products world...

"Don't take it serious... live and laugh at it all..."

"a bowl of cherries"

### Telecom Products World...

"a box of chocolates"

### Embedded Computing world...

"What we do today, might burn us tomorrow..."

"jar of jalapeños"

### Last year at ETT...

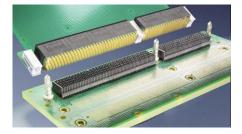

Original MULTIGIG RT 2 Contact Standard Guide Hardware Redesigned MULTIGIG RT 2-R Contact Standard Guide Hardware Redesigned MULTIGIG RT 2-R Contact Machined Guide Hardware

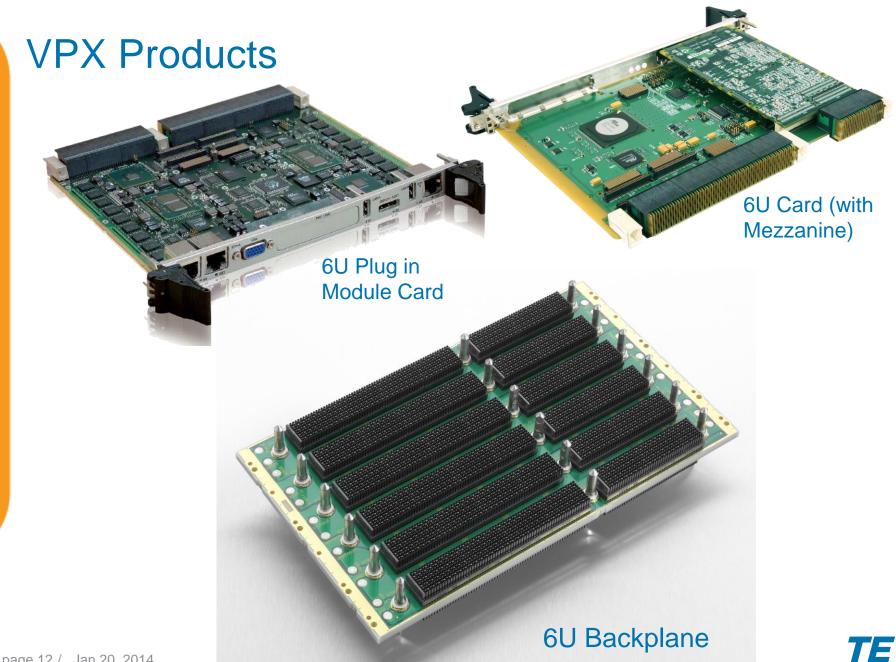

#### Expanding a strong foundation of rugged VPX products with RT 2-R

# The World of rapidly evolving high performance computing

• CPU's, GPU's, & FPGA's

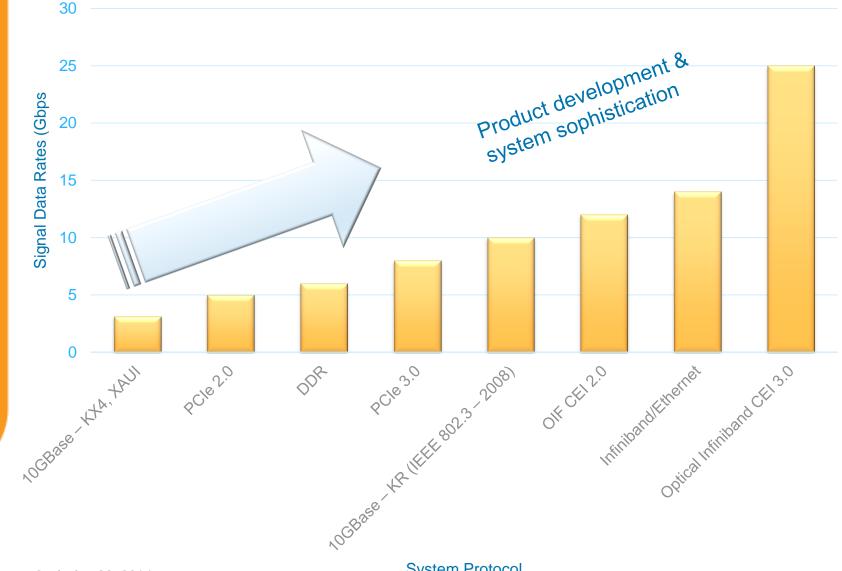

### **Protocols and Data Rates**

System Protocol

### System performance depends on...

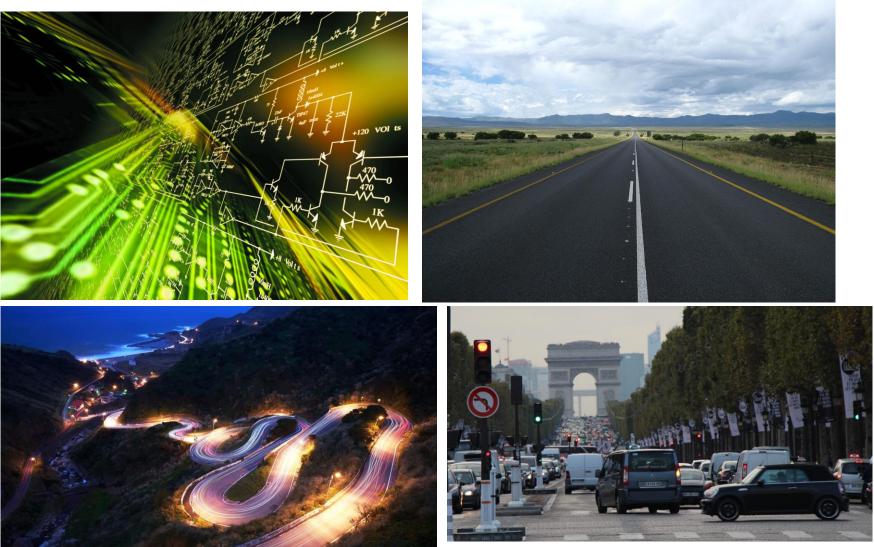

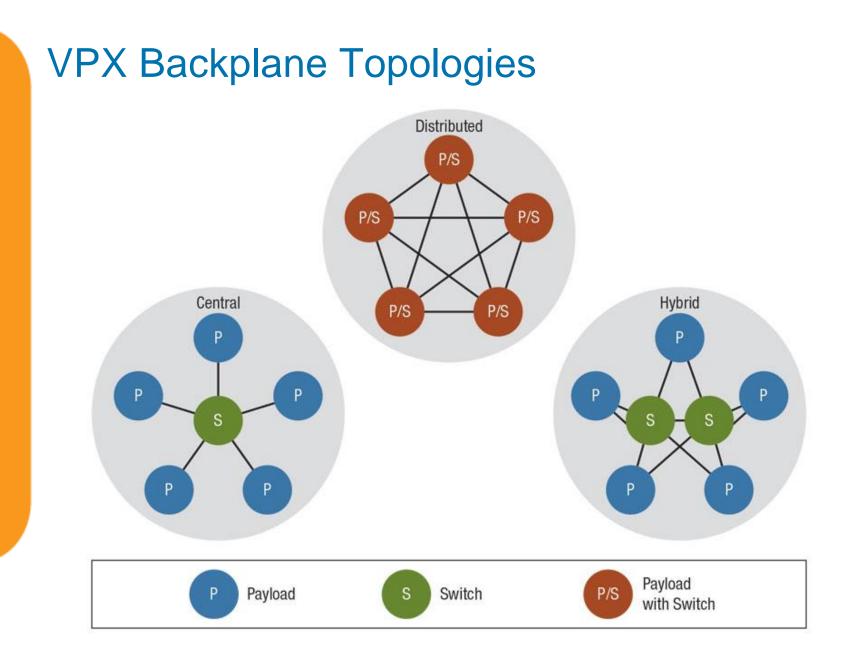

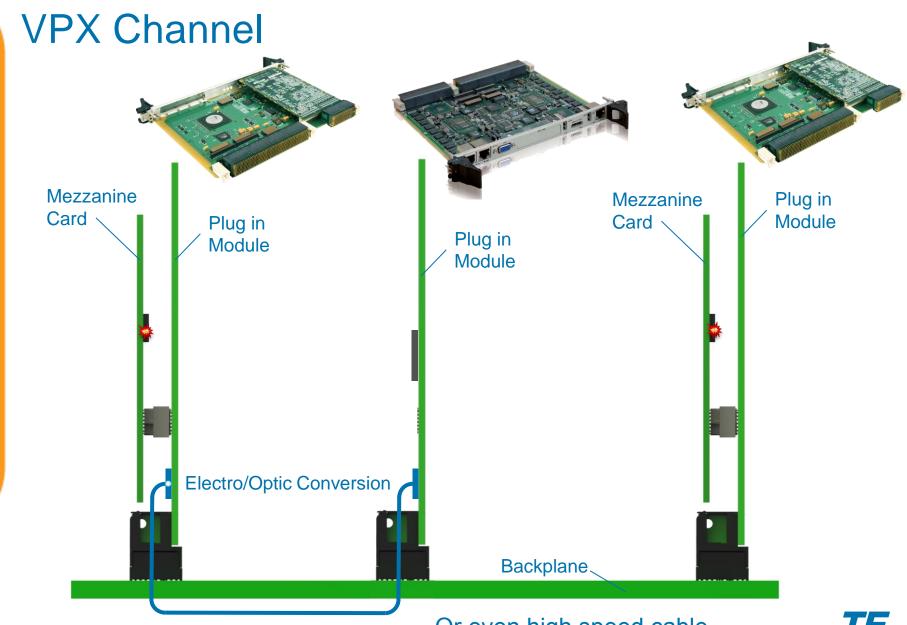

## What is the path of the circuit

page 10 / Jan 20, 2014

## What is the environment

page 14 / Jan 20, 2014

Or even high speed cable...

# Take Nothing for Granted

- Design Analysis

- 3D Electromagnetic solvers, S-parameter characterization

- Connections

- Improved connector footprints and via optimization

- Manufacturing

- Better PCB materials & no-stub techniques

- Backplane

- Data flow architecture and high speed routing rules

- Silicon Technology

- Passive & Active signal conditioning, multi-level encoding

- Equalization Techniques

- Decision feedback equalizer (DFE) & Forward Error Correction (FFE)

### **Copper Foil Definition**

#### Shiny Cu

- Matte (opposite drum side) towards laminate

- Shiny drum side towards prepreg

#### Standard Cu (S)

•IPC-4562A, no roughness designation

Laminate dielectric, Matte Cu surface

#### Low Profile and Very Low Profile Cu

- a.k.a. L or LP and V or VLP

- IPC-4562A, Max. LP profile 10.2μm (400 μin)

- IPC-4562A, Max. VLP profile 5.1μm (200 μin)

Laminate dielectric, Matte Cu surface

#### **Ultra Low Profile Cu**

- a.k.a. HVLP, VSP, VLP2, HSVSP, etc.

- IPC-4562A, No treatment or roughness

Laminate dielectric, Matte Cu surface

#### **Reverse Treat Cu**

- a.k.a. RTF, RTC, DSTF

- Matte (opposite drum side) AWAY from laminate

- Shiny drum side towards laminate

#### **RTF Standard Cu (S)**

IPC-4562A, no roughness designation

Laminate dielectric, Shiny Cu surface

#### **RTF VLP Cu**

- IPC-4562A, Max. LP profile 10.2μm (400 μin)

- IPC-4562A, Max. VLP profile 5.1μm (200 μin)

Laminate dielectric, Shiny Cu surface

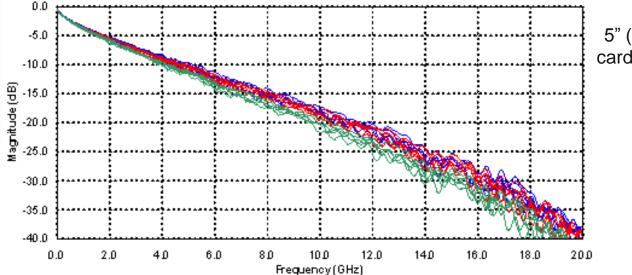

### **Typical Backplane Channel Insertion Loss**

| PCB Material    | Loss/in    | Loss @ 27" (0.7m) | Length @ -25dB |

|-----------------|------------|-------------------|----------------|

| Megtron 6 HVLP  | 0.75 dB/in | 20 dB             | 33" (0.8m)     |

| Megtron 6 HTE   | 1.0 dB/in  | 27 dB             | 25" (0.6m)     |

| Nelco 4000-13SI | 0.9 dB/in  | 24 dB             | 28" (0.7m)     |

5" (13cm) daughter card length 6mil trace

17" (43cm) backplane length 6mil trace

5" (13cm) daughter card length 6mil trace

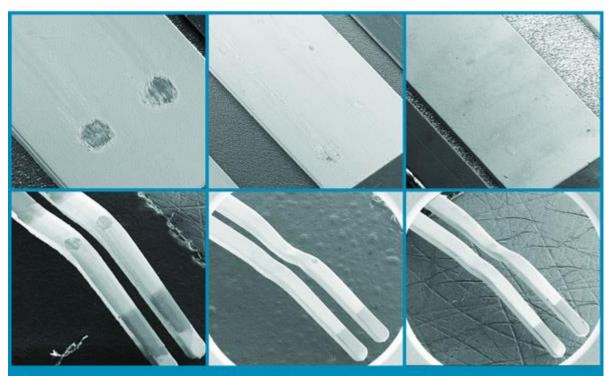

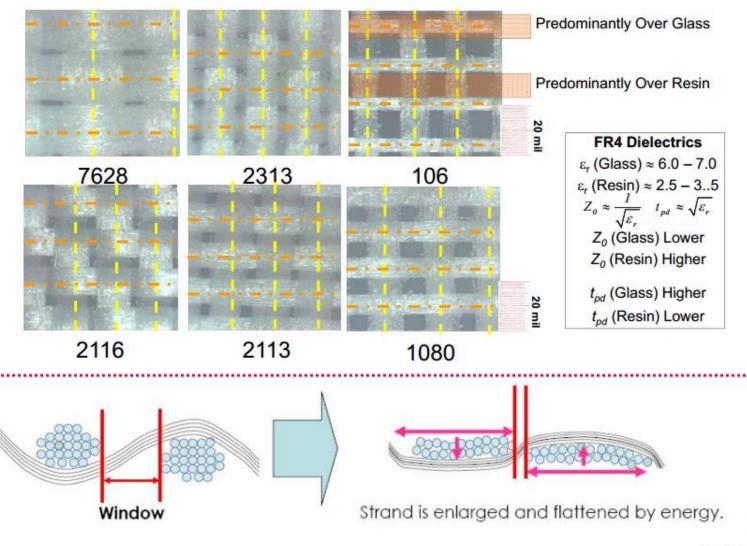

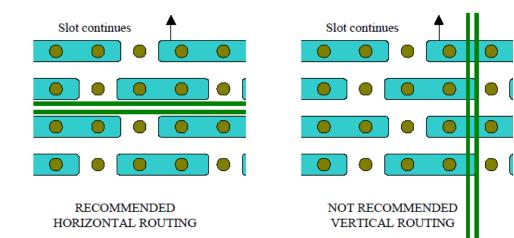

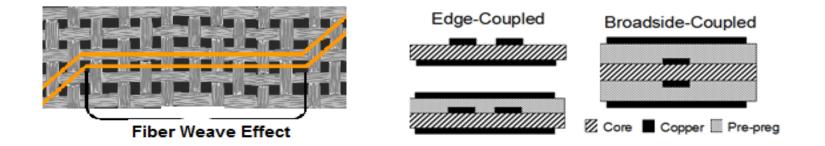

### **PCB Glass Weave effects**

SANMINA-SCI<sup>®</sup>

### **Differential Signal pair**

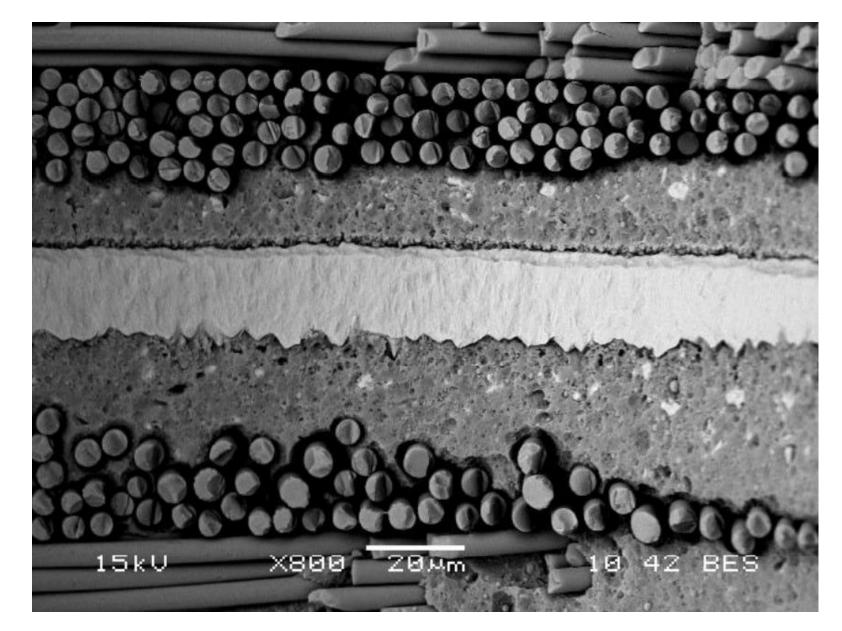

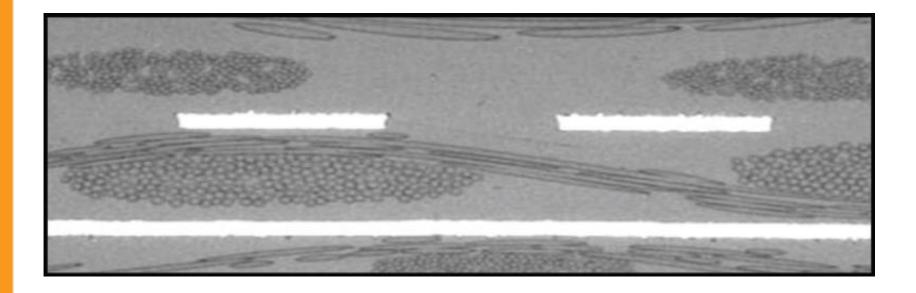

Cross section view of a differential signal pair with varying levels of fiber weave effect

page 20 / Jan 20, 2014

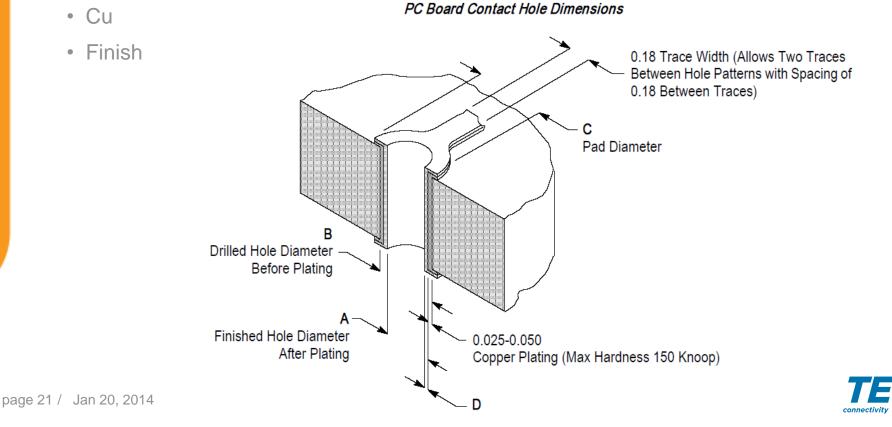

- PCB Fab technology

- Materials- (many choice\$)

- Via tolerances (must be compliant to MULTIGIG RT 2 App Spec 114-13056)

- \*Drill\* (most important, never compromise!)

- PCB Fab technology

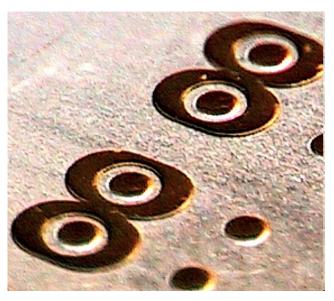

- Pad sizes

- Non-Functional Pads

- Antipads

- Size

- Shape

- PCB Fab technology

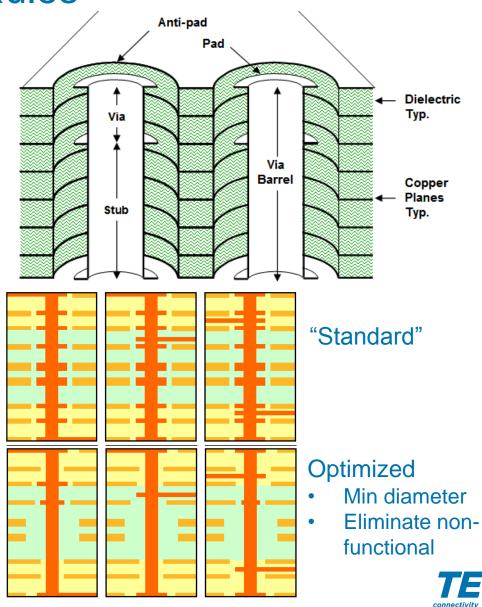

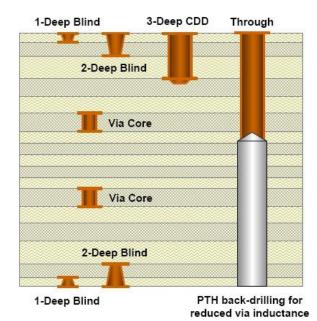

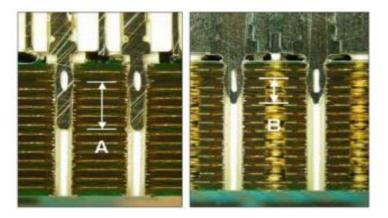

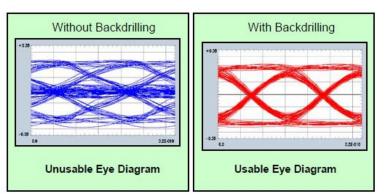

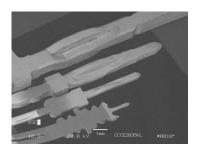

- Via Stub Control

- Counterboring

- Controlled Depth Drilling

- Blind Vias

10 mil via 10 mil Deep Layer 3 connection

Shaped 6 mil drill

6.25 Gb/s data rate

- PCB Fab technology

- Routing Channels

### Embedded Tech Trends in VPX

- Where things are going...

- Performance and reliability matters

- What can we do about it?

- -VITA 46 compliance

- Leap to alternate technology (F/O, etc.)

- Intermateable VPX derivatives with enhanced performance

• Know what we really **need**...Everything Matters!

### Readily Available studies on Via design for High Speed Signaling

- Agilent EEsof EDA, Presentation Designing a Transparent Via, 2007

- DesignCon 2012 Vias, Structural Details and their Effect on System Performance

- UltraCAD Design Note The Effects of Vias on PCB Traces

- Ravi Kollipara & Ben Chia Modeling, Verification of backplane Press-fit Vias

- Lambert Simonovich, Dr.Eric Bogatin & Dr. Yazi Cao Method of Modeling Differential Vias

- Sanmina SCI

- And many more .....

# **EVERY CONNECTION COUNTS**